手機半導體集成電路設計是現(xiàn)代電子工業(yè)的核心技術之一,它直接決定了智能手機的性能、功耗和功能多樣性。隨著5G通信、人工智能和物聯(lián)網(wǎng)的快速發(fā)展,手機芯片設計正面臨前所未有的挑戰(zhàn)與機遇。

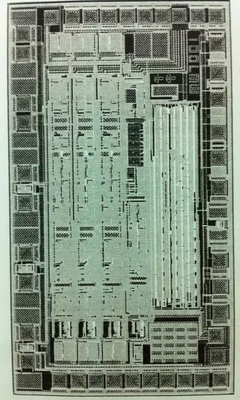

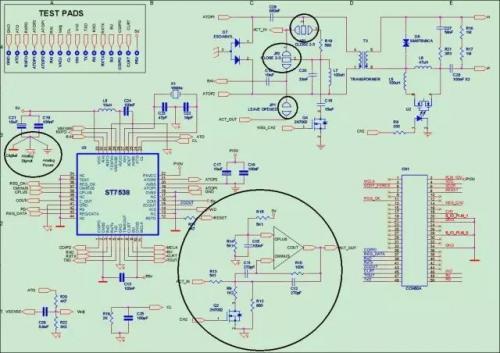

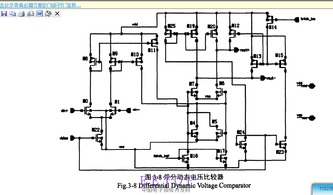

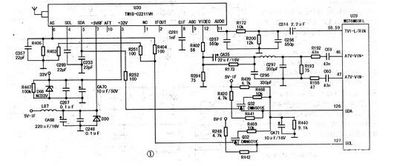

集成電路設計通常分為前端設計和后端設計兩大階段。前端設計包括架構規(guī)劃、邏輯設計和驗證,確保芯片功能符合預期;后端設計則涉及物理布局、時序分析和功耗優(yōu)化,直接影響芯片的制造成功率。在手機芯片領域,設計者還需特別關注射頻電路、圖像處理單元和基帶處理器的集成,以支持高速數(shù)據(jù)傳輸和多模通信。

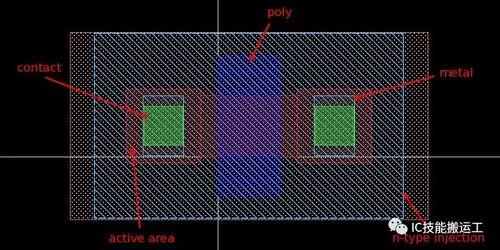

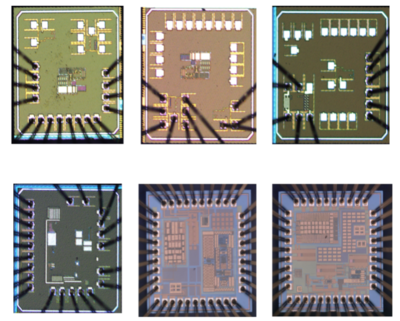

當前,手機半導體設計正朝著更小制程、更高集成度和更低功耗的方向發(fā)展。7納米、5納米乃至3納米工藝的逐步商用,使得單一芯片能夠容納數(shù)百億個晶體管,顯著提升了處理能力。同時,異質(zhì)集成技術允許將不同工藝的芯片(如CPU、GPU和內(nèi)存)封裝在一起,進一步優(yōu)化了性能與能效比。

未來,隨著量子計算、神經(jīng)擬態(tài)芯片等新興技術的成熟,手機集成電路設計或?qū)⒂瓉砀锩酝黄啤TO計者需持續(xù)創(chuàng)新,平衡性能、成本與可靠性,以推動智能手機產(chǎn)業(yè)的持續(xù)進步。